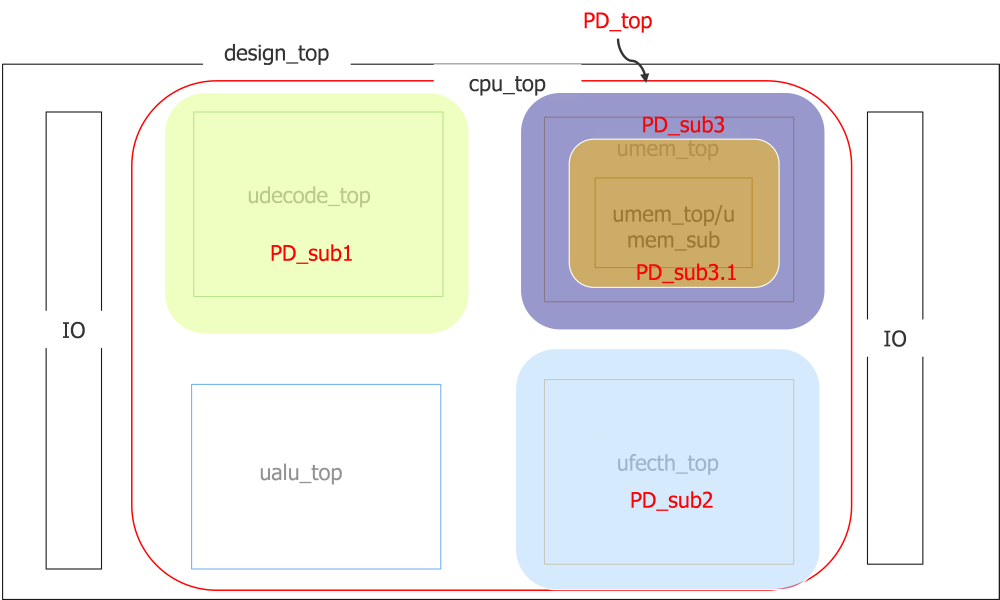

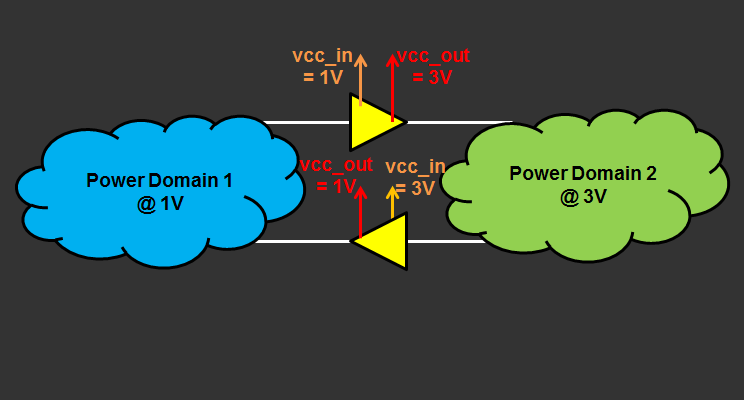

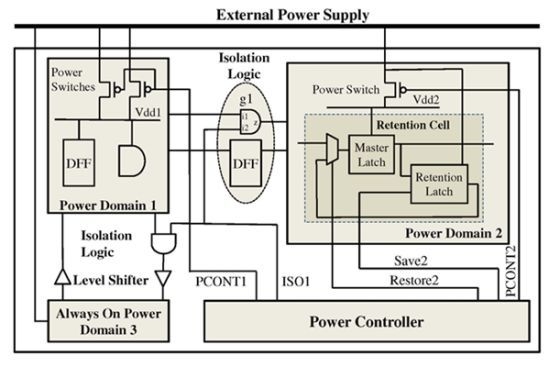

details the structure of the AO_PD (power domain 0) layer of Fig. 1.... | Download Scientific Diagram

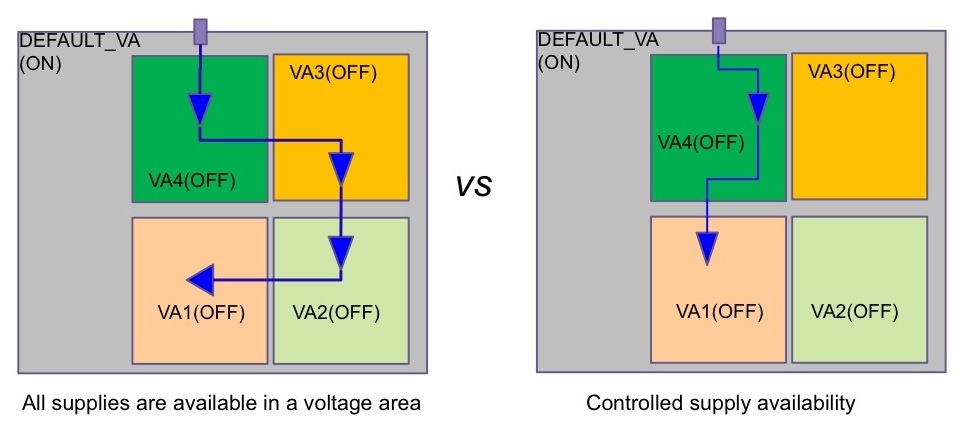

JLPEA | Free Full-Text | Low Power Testing—What Can Commercial Design-for-Test Tools Provide? | HTML

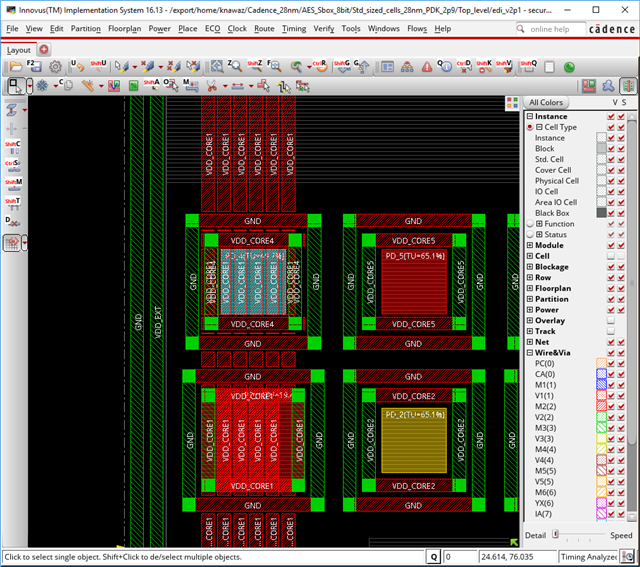

addStripe command for multiple power domains - Digital Implementation - Cadence Technology Forums - Cadence Community